LOGIC

All of the following logic constructs assume all inputs are binary with a voltage value of 0V (False) or 10V (True). If you have unconstrained analog inputs, you can use any of the Comparator constructs to convert them to binary before feeding them into a logic gate.

All of the logic constructs support polyphony. If all inputs are polyphonic, then the outputs will be polyphonic as well.

Most of the constructs include their own copy of an 8VERT to supply constant CV. But that can become wasteful if there are many logic gates in your patch. Feel free to patch in the needed constant CV from elsewhere and remove the redundant 8VERTs if you can.

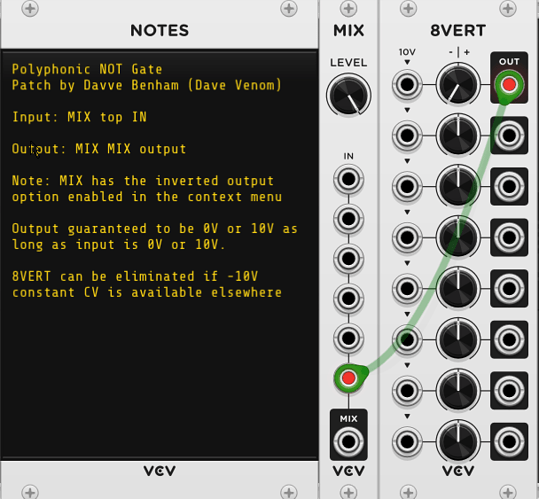

Polyphonic NOT Gate

VCV Fundamental Polyphonic NOT Gate.vcvs (2.0 KB)

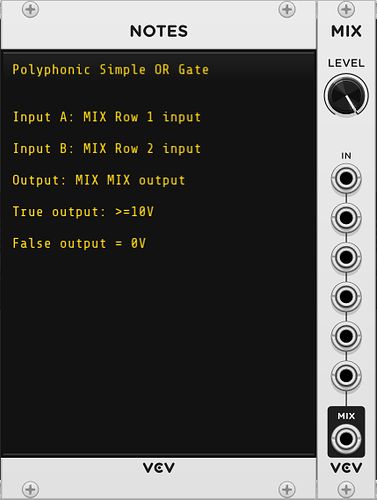

Polyphonic Simple OR Gate

It is “common knowledge” that a mixer can be used as a simple OR gate. However, the outputs are not restricted to 0V or 10V. This construct is included for completeness.

VCV Fundamental Polyphonic Simple OR Gate.vcvs (873 Bytes)

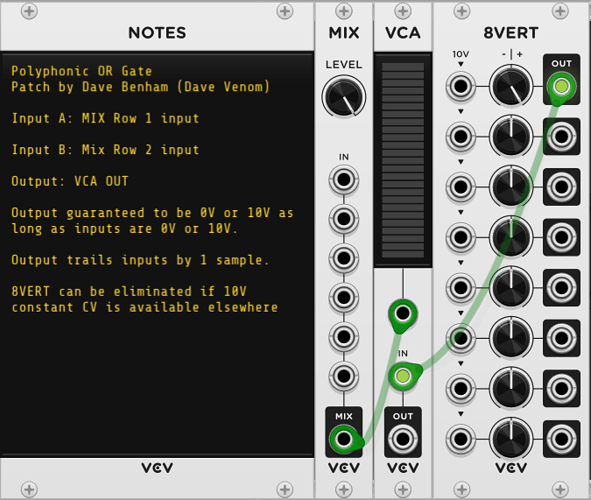

Polyphonic OR Gate

This slightly more complex version of an OR gate forces the output to be 0V or 10V.

VCV Fundamental Polyphonic OR Gate.vcvs (2.6 KB)

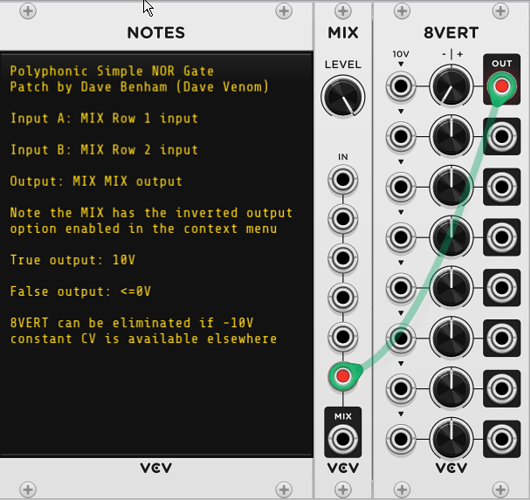

Polyphonic Simple NOR Gate

Like most of the logic constructs, the negated version simply appends NOT logic to the base construct. The simple NOR may have false outputs that are < 0V.

VCV Fundamental Polyphonic Simple NOR Gate.vcvs (2.0 KB)

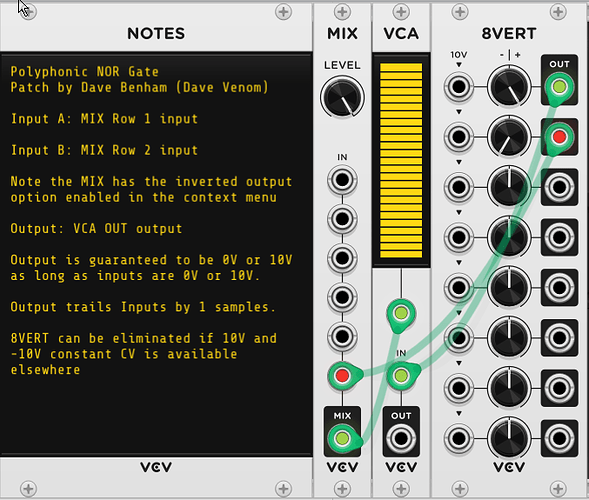

Polyphonic NOR Gate

Again, a bit more sophisticated version to force outputs to be 0V or 10V.

VCV Fundamental Polyphonic NOR Gate.vcvs (2.9 KB)

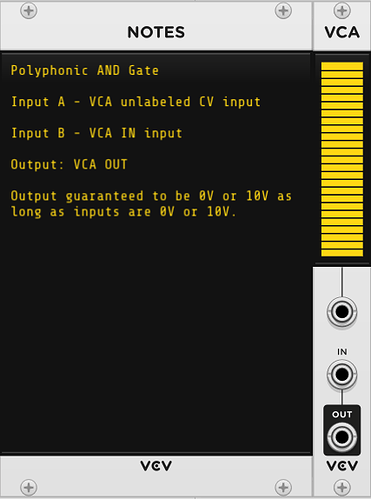

Polyphonic AND Gate

Another “common knowledge” construct that is included for completeness.

VCV Fundamental Polyphonic AND Gate.vcvs (876 Bytes)

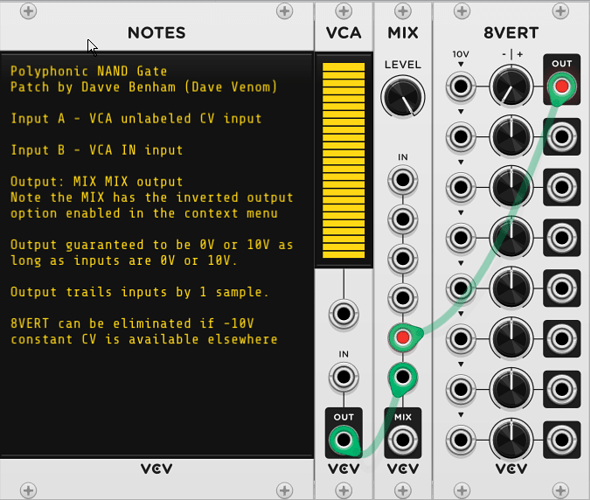

Polyphonic NAND Gate

VCV Fundamental Polyphonic NAND Gate.vcvs (2.7 KB)

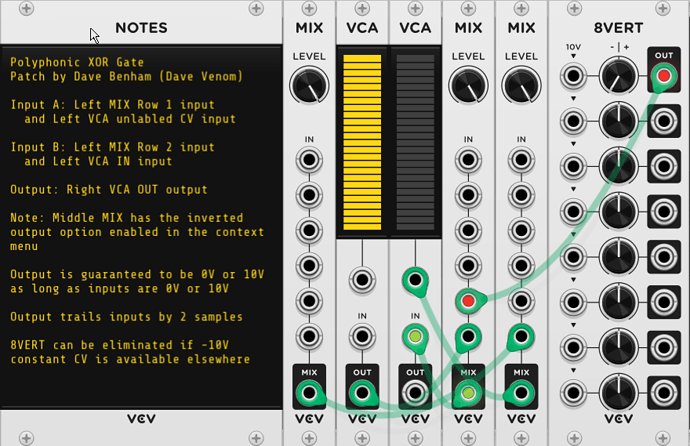

Polyphonic XOR Gate

An XOR gate can be created by combining OR AND NAND

VCV Fundamental Polyphonic XOR Gate.vcvs (4.6 KB)

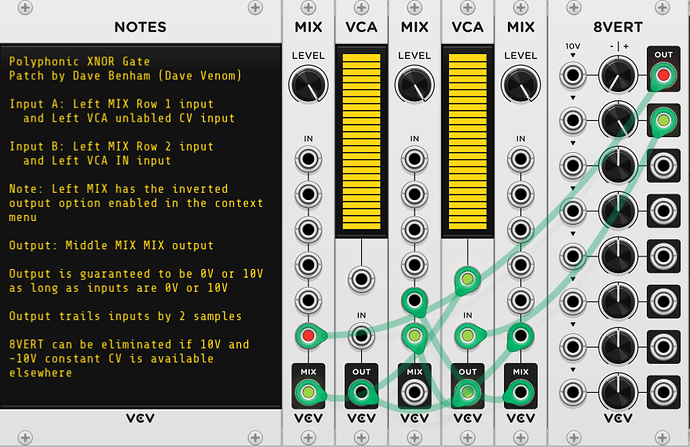

Polyphonic XNOR Gate

XNOR can be created by combining NOR OR AND

VCV Fundamental Polyphonic XNOR Gate.vcvs (4.8 KB)

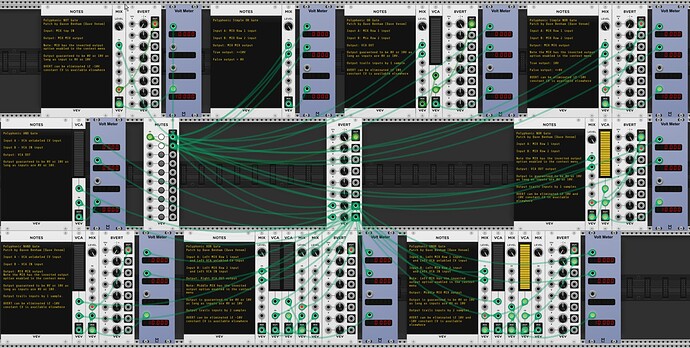

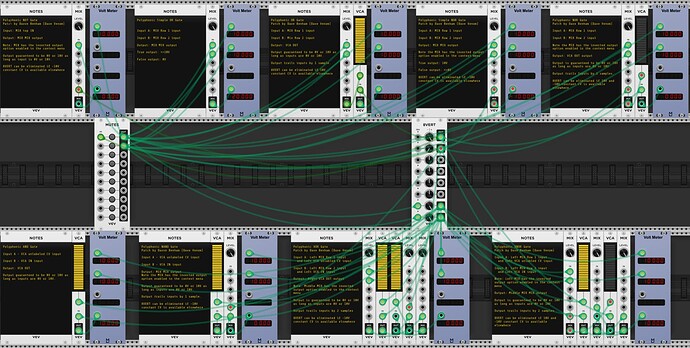

Trivial Logic Demo

The following patch demonstrates each of the logic gates. There are two versions of the demo.

- The version at the top includes the 8VERT for each logic gate.

- The version at the bottom shows how it might look if the gates share a common 8VERT.

For each version, the top two MUTES buttons represent the A and B inputs, with lit representing FALSE, and unlit TRUE. The ML Voltmeter next to each gate shows the current value for A and B at the top, as well as the resultant output at the bottom.

VCV Fundamental Logic.vcv (5.7 KB)