Adding a delay would not give the result you want because if you wait until after the 1 ms block, then it will advance the sequence to step 2.

But I am surprised that the clock pass through plays the 1st step without ORing with the reset signal. Or to be more precise, I don’t understand why there is a difference between standard mode vs. clock passthrough.

Clearly the sequence advance is blocked by the reset, else the clock passthrough would advance to the 2nd step, thus skipping step 1. But with standard mode, the reset also blocks the trigger output, but the reset does not block the clock passthrough output. That doesn’t make sense - they serve the same purpose, so I would expect the behavior to be the same. I’m curious if the difference is intentional.

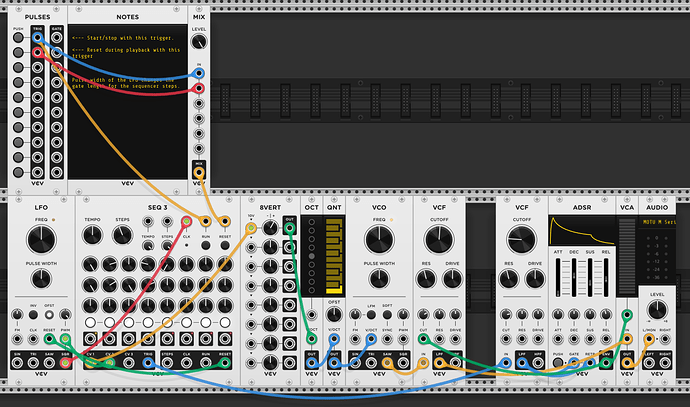

Absolutely, you can use one of the SEQ 3 CV channels to control the clock pulse width. But the VCV VCO cannot output 100% pulse width, so you might think it is impossible to tie beats together into a single gate. But there is one more trick available - just add a slew limiter so the momentary voltage dip does not go low enough to retrigger the ADSR. And you can still stay with pure VCV by using a low pass filter as a slew limiter.

I did just that in my 32 Step sequencer demo as part of my VCV Fundamental Constructs project.

Here is your patch modified a bit to modulate the PW with slew added so there is a tie from step 1 to 2, and 3 to 4. In other words the ADSR fires only on beats 1 and 3. Try increasing the frequency of the right filter and you will reach a point where all beats trigger the ADSR.

basic-sequencer-setup with ties.vcv (2.2 KB)