I use the falling edge of the last SEQ step GATE to increment the Sequential Switch - the cable adds 1 sample, the first gate may be little shorter - but that’s how I do it, when I’m too lazy to measure the timings. This method can be used for slow clocks OK i think - for faster clocks, use rising edge of last step + a sample delay, to get it “just right”, and switch just before the beginning of the first step.

(set SEQ-3 to “clock passthrough”)

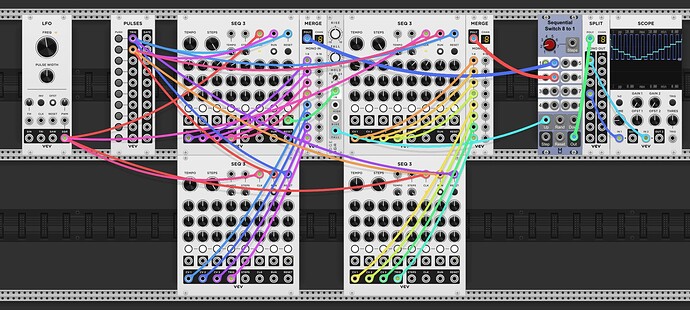

16 step 6CV + 2 gate setup:

4xSEQ3.vcvs (23.4 KB)