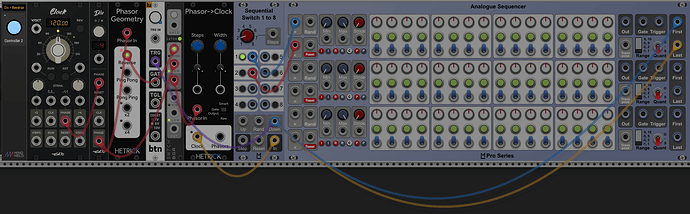

So the ML Sequencer has independent trigger inputs to go forward, or backward, or to a random step. But I gather you want the ability to step in a ping pong manner.

So for example, if you are only using steps 1 through 4, then you want the sequence to be

1, 2, 3, 4, 3, 2, 1, 2, 3, 4, 3, 2, 1, . . . . etc.

I believe @scook has some elements correct. But I see some potential problems (I don’t have the ML Sequencer, so I can’t test)

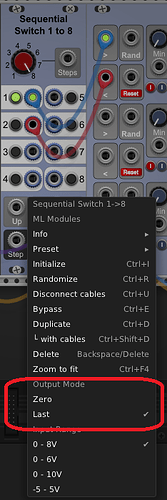

- I am pretty sure the Sequential Switch output mode should be set to 0, not last

- If the Sequential Switch is always triggered if either the sequencer First or Last gate is fired, then the sequencer could potentially oscillate between the first and last steps without ever going through the steps in between. To prevent that you only want the First gate to trigger the switch when the sequencer is currently stepping backward, and the Last gate to trigger the switch only when stepping forward.

- If the switch is triggered while the clock is still high, then the last (or first) switch will not go to completion because as soon as the switch changes, the clock will be sent to the opposite direction trigger and the last (or first) step will immediately exit.

Again, I computed all the above simply by running the logic through my head - I could not actually test anything. So I may have gotten something wrong.

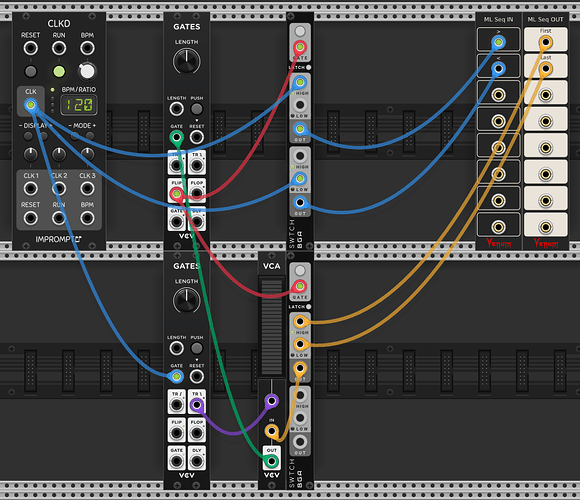

Either way, I believe the following will give the behavior you seek. In the image I am using the Bay Input and Output modules to represent the critical ML Sequencer inputs and outputs needed to implement the ping pong.

The top VCV GATES is operating as a flip flop to control the current direction state. When FLIP is high it represents a forward state, and when low then a backward state.

The top Bogaudio switch directs the triggering clock to the correct ML Sequencer trigger input, either forward or backward, depending on the flip flop state.

The ML Sequencer First and Last gates indirectly trigger the flip flop to change state. The bottom Bogaudio Switch controls which one is active. If currently moving forward, then only the Last gate matters. If moving backward, then the First gate matters.

But we don’t want the flip flop to change state while the triggering clock is still high. So the bottom VCV GATES converts the trailing edge of the clock gate into a trigger. The First or Last gate is only passed to the flip flop trigger when the clock trailing edge trigger AND First/Last gate are both high. So the VCA is functioning as an AND gate.

So lets say we are currently moving forward. Each time the clock fires, the gate is passed to the forward trigger input, and the sequencer moves to the next step. When the sequencer reaches the last step, the Last gate goes high. However, the clock is still high, so the flip flop is not yet triggered. When the clock goes low, the falling edge trigger is fired while the Last gate is still high, and the trigger is sent to the flip flop to change to a reverse state. But now the clock is still low, so the sequencer remains on the last step. Then on the next clock, the gate is sent to the backward trigger, and the sequencer starts running in reverse. The logic is similar once the sequencer reaches the First step so the flip flop reverses back to forward again.

I am pretty confident the above arrangement will work, unless I have misinterpreted your end goal.